(1)Vos, 输入失调电压,要注意它的值会跟着气温改变而发生很大的漂移。

(2)IB+, 同相端输入偏置电流,它流过同向端等效阻抗,构成一个差错电压。

(3)IB-, 反相端输入偏置电流,它流过反向端等效阻抗,构成一个差错电压。

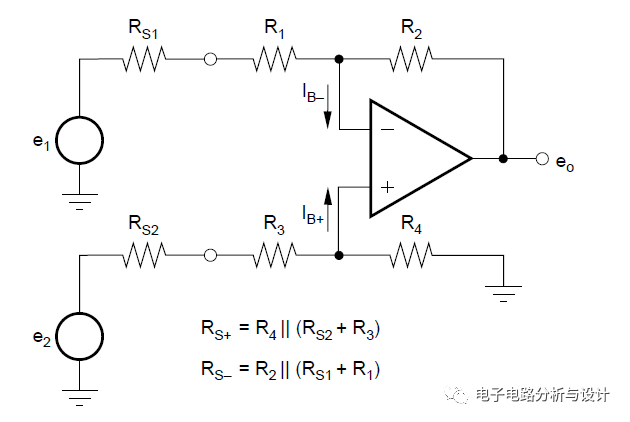

不过输入端阻抗RS+,RS-怎样核算呢?请见下图,可知输入端阻抗为信号源内阻+输入端份额电阻与反应电阻的并联(肯定不能疏忽信号源电阻,因为咱们经常选用高阻抗的传感器做信号源)。

不过为什么为并联,能这样了解:把信号源(电压源)e1,e2等效为阻值为零的电阻,则RS2、RS1左端相当于直接接地。关于同相偏置电流IB+别离经过R3+RS2、R4流向参阅地,因而RS+ = R4 (R3 + RS2)。

同理,IB– 别离经过R2和R+RS1流向参阅地(关于R2右端为什么能够等效为地,能够终究靠运放的低输出阻抗特性来了解,则R2右端能够近似为接地),因而RS– = R2 (R1 +RS1)。

(4)en, 等效输入噪声。这个值是由电压噪声,电流噪声和电阻热噪声三者构成的,是一切噪声等效到输入端的值。详细请参照Art Kay的文章和本系列博文的part4。

(5)eo/A, 这个表达式,或许很多人没有重视过,有这一项是因为运放的开环增益A不为0。这也便是为什么输出值不同,然后引起的等效输入差错不同的原因。

(6)eicm/CMRR, 这个不必多说,输入端的同模电压除以共模抑制比。又有一点欠好的当地,运放的CMRR是随共模信号频率的添加而下降的。好多运放的CMRR在共模信号到10KHz以上时,就比直流下降了几十个dB!

(7)ΔVs/PSRR,电源电压的改变引进的输入差错。相似的,PSRR在随频率的增高而下降。

看了这些,或许还会以为这些差错仍是很小的,在uV级,至多是mV级,不过不要忘了它还要乘上一个增益Gain。假设输入差错是100uV,增益为100倍,则输出的差错信号便是10mV。

假设还觉得没什么,那再讲一个经验值吧,一个满量程为5V的16位ADC的一个LSB约为75uV)。只需75uV的差错就会引起ADC的一位的改变,假设扩大电路的输出差错信号是1mV的话,这个信号给ADC,直接引起的差错便是13个LSB以上。

经过上面的剖析可知,咱们在规划电路时,应该依据详细的使用场合,挑选正真合适的运放并尽量减小直流差错。

电压;那么,输入阻抗怎样算呢?简言之,输入阻抗便是输入电阻(信号源电阻+输入端电阻)与反应电阻的并联。因为咱们一般都会选用高阻抗传感器做信号源,所以不能够忽视其电阻。参阅下图:

源 /

源 /

图 /

图 /

共模抑制比的影响 /

剖析 /

可从GraphQL查询生成Java模型的Apollo HarmonyOS

此外,张铠还一边

2023年法国I

PCB设计之前,

气动点焊机在焊接